# STUDY OF NOVEL CHANNEL MATERIALS USING III-V COMPOUNDS WITH VARIOUS GATE DIELECTRICS

Rakesh Prasher, Devi Dass and Rakesh Vaid<sup>\*</sup> Department of Physics and Electronics, University of Jammu, Jammu-180006, India prasher.rakesh@gmail.com; \*rakeshvaid@ieee.org

#### **ABSTRACT**

The exponential rise in the density of silicon CMOS transistors has now reached a limit and threatening to end the microelectronics revolution. To tackle this difficulty, group III–V compound semiconductors due to their outstanding electron transport properties and high mobility are very actively being researched as channel materials for future highly scaled CMOS devices. In this paper, we have studied a ballistic nanoscale MOSFET using simulation approach by replacing silicon in the channel by III-V compounds. The channel materials considered are silicon (Si), Gallium arsenide (GaAs), Indium arsenide (InAs), Indium Phosphide (InP) and Indium Antimonide (InSb). The device metrics considered at the nanometer scale are subthreshold swing, Drain induced barrier lowering, on and off current, carrier injection velocity and switching speed. These channel materials have been studied using various dielectric constants. It has been observed that Indium Antimonide (InSb) has higher on current, higher transconductance, idealistic subthreshold swing, higher output conductance, higher carrier injection velocity and comparable voltage gain compared to Silicon, thus, making InSb as a possible candidate to be used as channel material in future nanoscale devices.

### **Keywords**

Channel materials, III-V compounds, Nanoscale MOSFETs.

### **1. INTRODUCTION**

Latest International technology roadmap for semiconductors (ITRS) suggests that MOSFETs will reach sub-10 nm dimensions by 2016 [1]. However, to realize devices beyond the 45 nm technology node, novel device architectures along with high mobility materials are required for enhanced performances to improve the on-current and to reduce the power absorption [2-3]. Since the channel length has become comparable to the mean free path of the carriers in the inversion layer, the MOSFETs are expected to approach the ballistic transport mechanism and the ballistic current is affected by the channel material, wafer orientation and by the channel direction in the transport plane.  $I_{on}$  is given in terms of technological and channel material parameters by the following expression [4]:

$$I_{on} \simeq \frac{8qh}{3\sqrt{\pi}} \frac{(N_{inv})^{\frac{3}{2}}}{(n_v)^{\frac{1}{2}}(m_w)^{\frac{1}{4}}(m_L)^{\frac{3}{4}}}$$

(1)

where  $n_v$  is the valley degeneracy, while  $m_L$  and  $m_W$  are the effective masses in the direction of the channel length and width, respectively. The expression (1) reveals that the maximum I<sub>on</sub> can be obtained for the smallest transport masses and valley degeneracy. Therefore, III-V compound semiconductors such as GaAs, InP, InAs, InSb etc., should be explored as alternative channel materials in the future nanoscale devices [5-6].

A high mobility channel material has high injection velocity to increase the on-state current and reduces delay. Currently, strained-Si is the dominant technology for high performance

MOSFETs and increasing the strain provides a viable solution to scaling. However, looking into future scaling of nanoscale MOSFETs, it is important to look at higher mobility materials, like Ge and III-V compounds together with innovative device structures and strain, which may perform better than even very highly strained Si. For both Ge and III-V devices, problems of leakage need to be solved. Due to their extremely small transport mass leading to high injection velocity ( $V_{inj}$ ), III-V materials appear to be very attractive candidates as channel materials for highly scaled n-MOSFETs [7]. However, III-V materials have many significant and fundamental issues, which may prove to be severe bottlenecks to their implementation. Although their small transport mass leads to high  $V_{inj}$ , III-V materials have a low density of states (DOS) in the  $\Gamma$ -valley, tending to reduce the inversion charge ( $Q_{inv}$ ) and hence reduce drive current [8-9]. Furthermore, the small direct band gaps of Ge and III-V materials inherently give rise to very large band to band tunneling (BTBT) leakage current compared to Si. Despite of low inversion charge ( $Q_{inv}$ ), due to their large injection velocity ( $V_{inj}$ ), III-V materials like InAs, InSb and InP can flow up to 80% larger drive current than Si. The I<sub>OFF, BTBT</sub> in Ge, InAs, GaAs and InSb can be reduced by over ~1000X by scaling.

Various heteroepitaxy approaches and structures for advanced channel material fabrication in "On-Insulator (OI)" structures using global and localized epitaxy techniques with strained-Si. Ge, III-V etc. have been suggested by Cheng [10]. OI architectures offer many technological advantages and improve both CMOS scalability and current drivability. In addition, OI architecture can help reducing the high leakage current associated with many advanced materials. Room temperature hole mobility in a 7.5nm thick Ge quantum well has already been reported to exceed 2500 cm<sup>2</sup>/V-sec [11]. Recently, a great progress has been made to integrate high-k gate dielectric with Ge process and active research in this field is underway [12-15]. High performance, n- and p- channel Ge MOSFETs has been reported in [16-20]. Robust and highly manufacturable new process technologies, such as atomic layer deposition (ALD), heteroepitaxy and metal gates, have opened the opportunity to integrate III-V semiconductors with Si technology. With their exceptionally high mobilities, III-V materials display promise for ultra-fast, very low power digital logic technology. In [21-22], using ALD Al<sub>2</sub>O<sub>3</sub> as the gate insulator, GaAs MOSFETs with excellent performance was reported for the first time. Later, GaAs MOSFET with oxidized InAlP gate insulator was reported in [23]. Other III-V materials, InAs and InSb, also show great promise as novel channel material for logic technology due to their exceptionally high carrier mobilities. InSb is a fascinating material because its high electron mobility is appropriate for high speed transistors and Hall-effect devices. Its narrow band gap is also suitable for infrared applications. InSb can be directly grown on Si substrate without insertion of buffer layer and leakage current between InSb and Si Substrate is very small. Recently, for the first time, InSb based Quantum Well FET has been reported [24]. Fischetti et al. showed in [8] that indium based semiconductors can outperform Si and Ge MOSFETs in deeply scaled MOSFETs.

The main aim of this paper is to provide an insight by replacing Silicon in the channel by III-V compound semiconductors using different dielectric constants. A comparison of InSb has been made with InP, InAs, GaAs and Si. Various channel materials used along with their properties are shown in Table 1 whereas various input parameters as well as dielectric materials used in the simulations are shown in tables 2 & 3 respectively.

|                                                     |      | Compound Semiconductors |       |       |       |

|-----------------------------------------------------|------|-------------------------|-------|-------|-------|

|                                                     | Si   | InP                     | GaAs  | InAs  | InSb  |

| Electron mobility $(\mu_n) \text{ Cm}^2/\text{v-s}$ | 1450 | 5900                    | 9200  | 33000 | 77000 |

| Effective mass                                      | 0.19 | 0.077                   | 0.063 | 0.028 | 0.014 |

| Band Gap (eV)                                       | 1.12 | 1.34                    | 1.42  | 0.35  | 0.17  |

| Valley<br>degeneracy                                | 2    | 1                       | 1     | 1     | 1     |

Table 1. Cannel Materials used

Table 2. Parameters used for Simulation

| S.No | Input Parameters                     | Value                                |  |

|------|--------------------------------------|--------------------------------------|--|

| 1    | Insulator thickness                  | 5.00e-9                              |  |

| 3    | Temperature                          | 300 K                                |  |

| 4    | Threshold voltage                    | 0.32 ev                              |  |

| 5    | Gate control parameter               | 1.00                                 |  |

| 6    | Drain control                        | 0                                    |  |

| 7    | Voltage Loop<br>(for both Vgs & Vds) | Initial Bias =0 V<br>Final Bias=1.0V |  |

Table 3. Dielectric Materials used

| Dielectric Materials<br>used | Dielectric Constant<br>(k) |

|------------------------------|----------------------------|

| SiO <sub>2</sub>             | 3.9                        |

| $Si_3N_4$                    | 7.5                        |

| HfO <sub>2</sub>             | 20                         |

| ZrO <sub>2</sub>             | 25                         |

# 2. SIMULATION RESULTS AND DISCUSSIONS

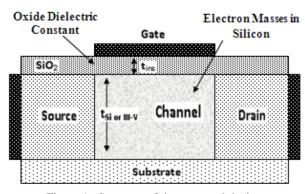

Figure 1 shows the structure of the simulated device. Various parameters used for the simulation are as listed in tables 1, 2 and 3. In this section we will discuss various simulation results obtained.

Figure 1. Structure of the proposed device

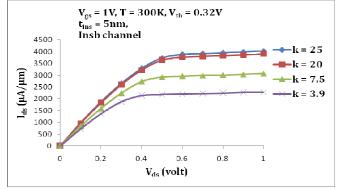

Figure 2 shows the  $I_{ds}$ - $V_{ds}$  characteristics for different dielectrics at constant  $V_{gs} = 1V$ ,  $t_{ins} = 5nm$  and InSb as channel material. Exact saturation occurs around 0.4V to 0.6V for all the dielectric materials. ZrO<sub>2</sub> has a high saturation voltage around 0.6V with highest saturation current. This figure further indicates that drain current increases with increase in drain voltage upto pinch-off voltage and beyond this point there is no effect of drain voltage over the drain current as happens in conventional MOSFETs.

Figure 2.  $I_{ds}$  – $V_{ds}$  characteristics

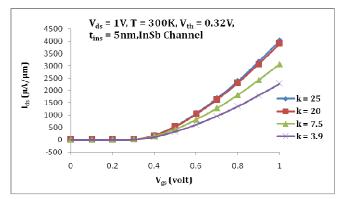

Figure 3.  $I_{ds}$ - $V_{gs}$  Characteristics

Figure 3 shows the  $I_{ds}$ - $V_{gs}$  characteristics for different dielectrics at constant  $V_{ds} = 1V$ ,  $t_{ins} = 5nm$  and InSb as channel material.  $ZrO_2$  has higher drain currents but requires lower threshold voltage. Thus, it is not possible to suppress subthreshold effects and quantum confinement cannot be achieved.

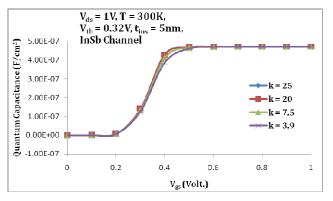

Figure 4 shows the quantum capacitance vs. gate voltage behavior for various dielectrics and InSb as channel material. The device can be operated at quantum capacitance limit when its gate capacitance is considerably higher than quantum capacitance. To know device operation at QCL limit, value of quantum capacitance at inversion, depletion accumulation region of the device,

Figure 4. Variation of Quantum Capacitance w. r. t. gate voltage for different dielectrics.

the study of  $Qc - V_g$  curves is necessary. For  $ZrO_2$  at low voltage (upto  $V_g = 0.2V$ ) quantum capacitance remains constant. SiO<sub>2</sub> has low quantum capacitance.  $ZrO_2$  has well defined accumulation and inversion regions with higher threshold voltage due its higher gate capacitance and quantum capacitance.

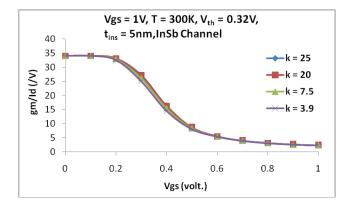

Figure 5 shows transconductance/drain current ratio  $(g_m/I_d)$  variations w. r. t. gate voltage for different dielectrics at constant  $V_{ds} = 1V$  and  $t_{ins} = 5nm$  and InSb as channel material. As the  $V_{gs}$  increases, the  $g_m/I_d$  decreases, in other words, the sensitivity of the device  $(g_m)$  by governing the equation,  $g_m = I_d/V_{gs}$ . As we know that the maximum performance is obtained when the value of  $g_m/I_d$  ratio also known as transconductance efficiency is the largest.  $ZrO_2$  has slightly higher value of  $g_m/I_d$  ratio than the other dielectric materials.

Figure 5. Variations of gm/Id w. r. t. gate voltage for different dielectrics.

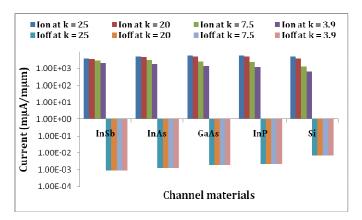

Figure 6:  $I_{on}$  and  $I_{off}$  for different channel materials.

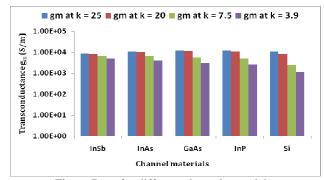

Figure 7: g<sub>m</sub> for different channel materials.

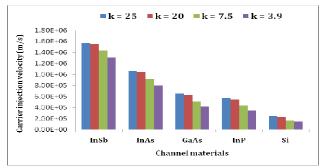

Figure 8: Vinj for different channel materials.

The bar graph in Figure 6 indicates that InSb has lowest  $I_{off}$  and highest  $I_{ON}$  current among other channel materials at various dielectrics. The switching speed ( $I_{on}/I_{off}$  ratio) is highest for InSb. Figure 7 suggests that InSb has higher transconductance than other channel materials for different dielectrics. Further, Figure 8 suggests that the carrier injection velocity or in other words, mobility of charge carriers in InSb is higher compared to the other channel materials for different dielectrics which give higher  $I_{on}$  current.

International Journal on Organic Electronics (IJOE) Vol.2, No.1, January 2013

### **3.** CONCLUSIONS

Based on the various results obtained, we conclude that InSb has higher on-current, lowest offcurrent for  $ZrO_2$  as dielectric material. It means the nanoscale MOSFET has fast switching speed. It has maximum carrier injection velocity due to high mobility and high current handling capability with low gate derives voltage for achieving high frequency response. It has subthreshold swing of 59.70 mV/decade (very close to practical value i.e. 60 mV/decade), and highest than other channel materials. Hence, we can say that InSb channel material enhance the device performance and could be used as novel channel material in future nanoscale devices.

## REFERENCES

- [1] http://www.public.itrs.net

- [2] B. Yu et al, (2001) "15 nm gate length planar CMOS transistor", *IEDM Technical Digest*, pp 937.

- [3] B. Doris et al, (2002) "Extreme scaling with ultra-thin Si channel MOSFETs", IEDM *Technical Digest*, pp267.

- [4] M. D. Michielis, D. Esseni and F. Driussi, (2007) "Analytical Models for the Insight into the Use of Alternative Channel Materials in Ballistic nano-MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 54, pp115-123.

- [5] J. A. Alamo, (2011) "Nanometre-scale electronics with III-V compound semiconductors", *Nature*, Vol. 479, pp317-323.

- [6] Y. Liu et al., (2010) "Fundamentals of III-V semiconductor MOSFETs", Springer, pp31-50.

- [7] R.Chau et al, (2005) "Benchmarking Nanotechnology for High-Performance and Low-Power Logic Transistor Applications" *IEEE Transactions on Nanotechnology*, Vol. 4, No. 2, pp153-158.

- [8] M. Fischetti et al, (1991) "Monte Carlo Simulation of Transport in Technologically Significant Semiconductors of the Diamond and Zinc-Blende Structures - Part II: Submicron MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 38, No. 3, pp650-660.

- [9] S. Laux, (2007) "A Simulation Study of the Switching Times of 22- and 17-nm Gate-Length SOI nFETs on High Mobility Substrates and Si", *IEEE Transactions on Electron Devices*, Vol. 54, No. 9, pp2304-2320.

- [10] Z. Y. Cheng, (2006) "Strained-Si and advanced channel materials on insulator: challenges and opportunities", *International Conference on Solid-State and Integrated Circuit Technology*, pp90-95,

- [11] M. Myronov et al, (2005) "Temperature dependence of transport properties of high mobility Holes in Ge quantum wells", *Journal of Applied Physics*, Vol. 97, pp6.

- [12] C. Chui et al, (2002) "Germanium MOS capacitors incorporating ultrathin high-k gate dielectric", *IEEE Electron Device Letters*, Vol. 23, No. 8, pp473-475.

- [13] C. Chui et al, (2003) "A germanium nMOSFET process integrating metal gate and improved hik dielectrics", *IEEE IEDM Technical Digest*, pp18.3.1-18.3.4.

- [14] D. Chi et al, (2004) "Zirconia grown by ultraviolet ozone oxidation on germanium (100) substrates", *Journal of Applied Physics*, Vol. 96, No. 1, pp813-819.

- [15] C. Chui, H. Kim, P. McIntyre and K. Saraswat, (2004) "Atomic layer deposition of high-k dielectric for germanium MOS applications – substrate", *IEEE Electron Device Letters*, Vol. 25, No. 5, pp274-276.

- [16] M. Lee et al, (2001) "Strained Ge channel p-type metal-oxide-semiconductor field-effect transistors grown on Si<sub>1-x</sub>Ge<sub>x</sub>/Si virtual substrates", *Applied Physics Letters*, Vol. 79, No. 20, pp3344-3346.

International Journal on Organic Electronics (IJOE) Vol.2, No.1, January 2013

- [17] H. Shang et al, (2002) "Electrical characterization of germanium p-channel MOS- FETs", *IEDM Technical Digest*, pp441-444.

- [18] H. Shang et al, (2003) "Electrical characterization of germanium p-channel MOSFETs", *IEEE Electron Device Letters*, Vol. 24, No. 4, pp242-244.

- [19] C. Chui, F. Ito and K. Saraswat, (2004) "Scalability and electrical properties of germanium oxynitride MOS dielectrics", *IEEE Electron Device Letters*, Vol. 25, No. 9, pp613-615.

- [20] A. Nayfeh et al, (2005) "Fabrication of high-quality p-MOSFET in Ge grown heteroepitaxially on Si", *IEEE Electron Device Letters*, Vol. 26, No. 5, pp311-313.

- [21] P. Ye et al, (2003) "GaAs metal oxide semiconductor field-effect transistor with nanometer-thin dielectric grown by atomic layer deposition", *Applied Physics Letters*, Vol. 83, pp. 180-182.

- [22] P. Ye et al, (2003) "GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition", *IEEE Electron Device Letters*, Vol. 24, No. 4, pp209-211.

- [23] X. Li, Y. Cao, D. Hall, P. Fay, B. Han, A. Wibowo and N. Pan, (2004) "GaAs MOSFET using InAlP native oxide as gate dielectric", *IEEE Electron Device Letters*, Vol. 25, No. 12, pp772-774.

- [24] T. Ashley et al, (2005) "Novel InSb-based quantum well transistors for ultra-high speed, low power logic applications", *International Conference on Solid-State and Integrated Circuits Technology Proceedings*, Vol. 3, pp2253-2256.

### Authors

Mr. Rakesh Prasher received his B.Sc Electronics from Govt. P.G. M.A.M College, Jammu, and the M.Sc Electronics from University of Jammu. He also received his M. Phil degree in Electronics from University of Jammu under the supervision of Dr. Rakesh Vaid. Presently he is pursuing Ph. D. from University of Jammu. His research interests include nano-devices such as nano-MOSFETs, nanowire based MOSFETs, etc and has more than 12 publications in national/ international conferences and journals.

Mr. Devi Dass received his B.Sc Electronics from Govt. P.G. M.A.M College, Jammu in 2007 and the M.Sc Electronics from University of Jammu, in 2009. He has also received his M. Phil degree in Electronics from university of Jammu under the supervision of Dr. Rakesh Vaid. Now, he is working for the Ph.D. degree at University of Jammu, Jammu. He has more than 15 publications in national / international conferences and journals.

Dr. Rakesh Vaid received his M.Sc. in Electronics from University of Kashmir with gold medal and Ph.D. in Electronics from the University of Jammu. Presently working as an Associate Professor in Dept. of Physics and Electronics at University of Jammu, India. His area of research includes device modeling and simulation of power semiconductor devices, Floating Islands and Trench gate technology, carbon nanotubes, graphene electronics besides devices like FinFET, exploring the new channel materials for nano scale MOSFETs. He has more than 50 publications in national/ international conferences and journals.