## TIME CRITICAL MULTITASKING FOR MULTICORE MICROCONTROLLER USING XMOS<sup>®</sup> KIT

Prerna Saini<sup>1,</sup> Ankit Bansal<sup>2</sup> and Abhishek Sharma<sup>3</sup>

# <sup>1,3</sup>Department of Electronics and Communication Engineering, LNM Institute of Information Technology, Jaipur, India

<sup>2</sup>Department of Electronics and Communication Engineering, GLA University, Mathura, India

#### ABSTRACT

This paper presents the research work on multicore microcontrollers using parallel, and time critical programming for the embedded systems. Due to the high complexity and limitations, it is very hard to work on the application development phase on such architectures. The experimental results mentioned in the paper are based on xCORE multicore microcontroller form XMOS<sup>®</sup>. The paper also imitates multi-tasking and parallel programming for the same platform. The tasks assigned to multiple cores are executed simultaneously, which saves the time and energy. The relative study for multicore processor and multicore controller concludes that micro architecture based controller having multiple cores illustrates better performance in time critical multi-tasking environment. The research work mentioned here not only illustrates the functionality of multicore microcontroller, but also express the novel technique of programming, profiling and optimization on such platforms in real time environments.

#### **Keywords**

Multicore microcontroller, xCORE, xTIMEcomposer, Multitasking, Parallel programming, Time slicing, Embedded System, Time critical programming.

#### **1.INTRODUCTION**

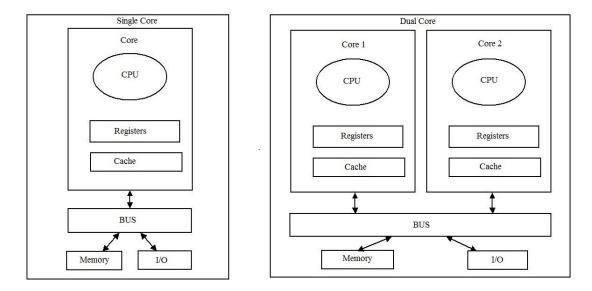

In the present era of technology, computational power [1] plays an important role. The multicore microprocessor devices [2] are already available in CISC architecture which used to perform non real time computing. Recently there has been a huge demand of high computing speed in time critical system, mostly in real time embedded device. Technology is growing exponentially every day with the demand of more power and processing handling capabilities. The basic need of a multicore system is the distributed and parallel computing [3]. Time consumption is the drawback of single core processors, so multicore [4] technology is used to achieve efficiency through parallel processing. Parallel processing [5] is the simultaneous use of more than one CPU to execute a program or multiple computational threads. The main goal of parallel processing is a high performance [6] computing, which speedup the execution time of the program. Parallel [7] processing makes programs run faster because there are more engines (CPUs or cores) workingon it. It increases the efficiency, safe execution time, take less energy and retain the time. Multicore has two or more CPUs while the single core has only one core inside it as illustrated in figure1. To enhance the performance [8] of single core processor, it is mandatory to increase the frequency as CPU load increases. It causes heat losses and leakage current so rather than increase the clock frequency of single core, manufacture switched to multicore to avoid the power [9] consumption problem and to increase speed and efficiency.

Figure 1. Block Diagram of Single-core and Multi-core Processor

As the number of the taskis rapidly increasing user wants to perform more than one task at a time, but a computer with a single-core performs one operation at a time [10]. Although with software threads, some amount of parallelization is possible, but it does not give satisfactory results. In multicore scenario, it is possible to perform operations at comparatively high speed [11] to perform paralleled task and save time. Table 1 represents the difference between single core and multicore and shows that multicore has more advantage over single core with respect to processing speed, power and operation handling ability etc.

| Parameter   | Single-Core        | Multi-Core                |

|-------------|--------------------|---------------------------|

| No of cores | One primary core   | Two or more separate core |

| Processing  | Sequential         | Parallel                  |

| SMT         | Not Possible       | Possible                  |

| Power       | Low                | High                      |

| Speed       | Slow               | Fast                      |

| Efficiency  | Low                | High                      |

| Operation   | One task at a time | Multitasking              |

Table 1. Comparison between single core and multi core system

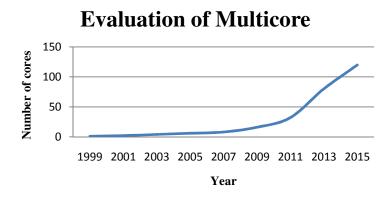

The multi-processing system has two types, namely homogeneous and heterogeneous. If all the cores are identical and have the same features like message passing system, cache, threading, share memory and resources then it is called homogeneous multi-core processors. In heterogeneous [12] systems all the cores have different features; it can vary clock cycles according to system requirements to achieve low power or ultra-low power mode.Flynn's taxonomy is a specific classification of parallel computer architectures that are based on the number of concurrent instruction (single or multiple) and data streams (single or multiple) available in the architecture [13]. Figure2 shows the evolution of multicore era thatevery single processor replaced by a multicore processor to get high performance [14]. At the present time, there is vast use of multicore [15] system. In future, no filed will be untouched with multicore system.The first dual core microprocessor was Power-4 [16], [17] which was designed by the IBM<sup>®</sup> in 2001.

Figure 2. Evaluation Era of Multicore system

Amdahl's law [18] is used to find out the speedup of a multicore system. Speedup is how much time taken by a program to execute through the single core divide by the time taken by a program when n number of processors execute in parallel manner as illustrated in equation 1 and 2 which shows that as the number of cores in a processor is increased, the speed of a system is also enhanced, but it is impossible to fully parallelize the program. Suppose a program takes 10 hours using single core and a particular portion of that program which cannot be parallelized take at least 1 hour, then by increasing the number of cores, execution time and speedup of the system cannot be changed. By increasing the number of cores somehow speed up is increased, but it depends upon how much a program can be parallelized.

$$T(n) = T(1)\left(B + \frac{1}{n}(1-B)\right) \qquad \dots (1)$$

$$S(n) = \frac{T(1)}{T(n)} = \frac{T(1)}{T(1)\left(B + \frac{1}{n}(1-B)\right)} = \frac{1}{B + \frac{1}{n}(1-B)} \qquad \dots (2)$$

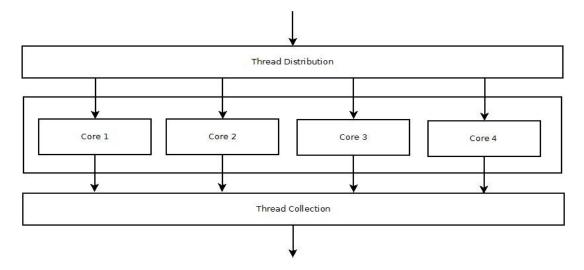

In parallel processing [19], every core executes the multiple set of instructions as an individual processing unit. The CPU istreated as a single unitso the end user can divide the whole task into subsection and send to various cores. Due to parallel processing all the core work simultaneously so it enhances processing speed and save the time. Important of parallelism is increased because complex problems can be split into smaller programs that can be executed at the same time to reduce execution time. Basically parallelism is subdivided in two broad areas i.e. Instruction level parallelism (ILP) and threads level parallelism. ILP tells, how many simultaneous instructions can be executed, and thread level parallelism (TLP), is about how many simultaneous threads can be executed. In a multicore system Parallelization is possible because it split threads and assigns it to each core and all works simultaneously. Execution within a processor is very quick and inexpensive for the time. Task parallelism is shown in figure 3.

International Journal of Embedded systems and Applications(IJESA) Vol.5, No.1, March 2015

Figure 3. Multithreading in multicore systems

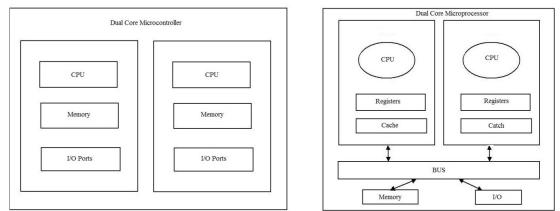

The microprocessor has only CPU, it does not have RAM, ROM and other peripheral on the chip, but the microcontroller contain all the basic components as shown in figure 4. A microcontroller has two kinds of design mechanics, i.e. UMA (Unified Memory Architecture) and NUMA (Non Unified Memory Architecture), although it can also be distinguished by Single Instruction Multiple Data (SIMD) and Multiple Instruction Multiple Data(MIMD). Table 2 illustrated the difference between microcontroller and microprocessor which show that the microcontroller has more advantage over microprocessor.

| Parameter           | Microcontroller          | Microprocessor               |

|---------------------|--------------------------|------------------------------|

| Meaning             | Computer on chip         | CPU on chip                  |

| Inbuilt components  | CPU, Memory & Peripheral | CPU ONLY                     |

|                     | Unit                     |                              |

| Memory Architecture | UMA                      | UMA and NUMA                 |

| Purpose             | Specific                 | General                      |

| Chips               | All components on chip   | Multiple chip for components |

| Circuit             | Simple                   | Complex                      |

| No of Registers     | More                     | Less                         |

| Operation           | Registers based          | Memory based                 |

| Clock Frequency     | Low                      | High                         |

| Cost                | Low                      | High                         |

| Speed               | Fast                     | Fastest                      |

Table 2. Difference between microcontroller and microprocessor

There are vast applications of multicore microprocessors. The market trends show that in general purpose computing processors are playing a key role. The entire major manufacturer is deploying their Integrated Circuit(IC) with its functionality. Processors are designed for general purpose; it can't be used in embedded application for that user need multicore microcontroller. Multicore microcontroller [20] is used in embedded application and Real Time Operating System(RTOS) in which time is a major factor. In real time application multicore microcontroller play a major role. In all major time critical operations, including defence, military, medical, industrial, etc. handled by multicore microcontroller. Recently mangalyaan launched in Indiain Mars orbit in low cost is

4

International Journal of Embedded systems and Applications(IJESA) Vol.5, No.1, March 2015

managed by multicore microcontroller. Table 3 compares the multicore microcontroller and multicore microprocessor and show that multicore microcontroller has a huge advantage over multicore microprocessor.

Figure 4. Illustrating Multicore Microcontroller vs Multicore Microprocessor

| Parameters             | Multicore Microcontroller    | Multicore Microprocessor        |  |

|------------------------|------------------------------|---------------------------------|--|

| Architecture           | Harvard                      | Von Neumann                     |  |

| Instruction Set        | RISC                         | CISC                            |  |

| Power                  | M Hz                         | G Hz                            |  |

| Execution time         | In nano sec or micro sec     | In milisec or in sec            |  |

| Cost                   | Chip                         | Expensive                       |  |

| Interrupt              | Given by the program         | Hardware and Software Interrupt |  |

| Priority               | Not define, All are executed | Masskable and Non Maskable      |  |

|                        | parallel                     |                                 |  |

| Cache                  | Not used                     | Used                            |  |

| Tile                   | Define                       | Not define                      |  |

| Time Critical Analysis | Can be done                  | Can not done                    |  |

| Power conception       | Low                          | High                            |  |

| Power Saving Mode      | Available                    | Not Available                   |  |

| Application            | Embedded system and RTOS     | General purpose                 |  |

Table 3. Distinction between multicore microcontroller and multicore microprocessor

### 2. XMOS<sup>®</sup> STARTKIT

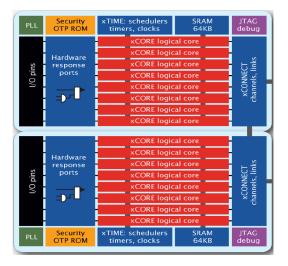

startKIT [21] is a xCORE multicore microcontroller that has eight 32 bit logical processor cores on two tiles as shown in figure5 which is taken from XMOS<sup>®</sup> XS architecture [22]. The size of startKIT is very small. The startKIT dimensions are 94 x 50mm. The startKIT require 5V which are given by Micro-USB cable. The regulator is used to convert this 5V to 1V and 3V which is used by external devices. Table 4 gives the overview of startKIT. It is very easy to use and simple to program. User can easily design complex embedded system using high level language. Each core acts as separately and able to run multiple real time tasks simultaneously. It provides 500 million instructions per second (MIPS) which make this more powerful than conventional microcontroller. It provides a uniquely scalable, timing deterministic architecture that provides extremely low latency and an I/O response that is 100 times faster than standard processors. If a core is waiting for data, the xTIME hardware scheduler will pass the execution resource to the next core making efficient use of the available processor resource and saving power.

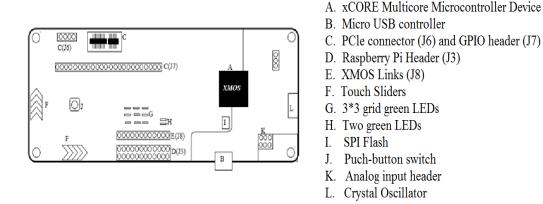

XMOS<sup>®</sup> provides xTIMEcomposer [23] IDE for designing applications. It supports high level languages like C,C++, XC (extension of C). It has inbuilt debugger, compiler, simulator and editor. xTIMEcomposer provide many functionalities to improve the performance and check various parameters like time, delay. xTIMEcomposer provide XMOS<sup>®</sup> Timing Analyser (XTA [24]) tool which allow developers to identify worst case and best case execution time for code blocks and functions. It also provides xSCOPE [25] which allow capturing the data from running time. Figure 6 explains the architecture of XMOS<sup>®</sup> startKIT. startKIT has two tiles. Tile 0 is dedicated to the integrated debugger and Tile 1 is user-programmable. It has 8 cores with 500 MIPS. Micro-USB connector (B) is used as a debugger. It connects to the host PC and allows running the program.

Dimension

No of Core

No of Tiles

32 Bit Word Length RISC Architecture Cache Not Used Clock Freq. 500 MHz SRAM 64 KB FLASH 256K Bytes 5V, 3V3, GND Voltage Programming High Level Language Language

94 x 50mm

8

Table 4. XMOS<sup>®</sup> startKIT overview

Figure 5. XMOS<sup>®</sup> architecture [22]

startKIT provide GPIO pins which allow developers to reconfigure the capabilities of devices to support many different applications. PCle slot is used to extend the hardware capabilities, 1\*5 PCIs connected (J6) and 1\*12 GPIO header (J7) is used to connect external hardware or peripheral. If PCIs slot is not used, then the user can use GPIO header [26]. The startKIT is compatible with the Raspberry Pi connection. The developer can connect Raspberry Pi board with startKIT using 2\*13 Raspberry Pi headers. It is compatible with Raspberry Pi [26] connection. It disables the LED and push button so the usercannot use LED and button in the Raspberry Pi header. XMOS<sup>®</sup> Links (E)1x13 pin GPIO header (J8) used for connecting multiple startKITs together. The startKIT provides two and four-zone capacitive touch slider which is illustrated as an F in figure 6. The startKIT has nine 3\*3 green LED as shown in section G. ThestartKIT has two additional green LED as a display in H.It has 256 KBytesof Serial Peripheral Interface (SPI) FLASH memory (I), which can be configured by the program.startKIT has one push button (J) which used as input and its status can be checked by software.startKIT provide 2\*3 analogy input header (K) which is used to give analogyinput.Tile 1 is clocked at 500 MHz, and the I/O ports are 100MHz. The startKIT board is clocked at 24MHz by a crystal oscillator as shown in L.

Figure 6. Architecture [24] of XMOS<sup>®</sup> startKIT

### 2.1. TASK PARALLELIZATION IN XMOS<sup>®</sup> STARTKITARCHITECTURE

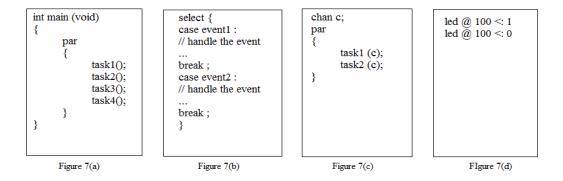

XMOS<sup>®</sup> [27] use 'par' constructs which allow several tasks to run parallel as illustrated in figure 7 (a) [27]. The compiler automatically checks how many cores are used and allocates the one task to one core whichever is free. The user can assign the task based on event occurs. XMOS<sup>®</sup> used 'select' keyword as illustrated in figure 7 (b) [27] which pause the task and wait for the event to occur and handle the event which isoccurring which is used as an interrupt. The event is assigned by the function of interrupt service routine (ISR). Multicore system also allows channelling and time stamping. Time stamping manages multiple events with a microcontroller that all require different timing. For example, you might want to control a servomotor (which requires a 20 millisecond delay), blink an LED once a second, and read some sensors (which should be read as frequently as possible. One way to handle this is to keep track of a time stamp for each event. The channel is used to communicate between the tasks. The user performs tasks parallel with shared memory. It creates a hang up situations when both the process tries to change or use the same data at the same time. Channel [27] resolves this issue. It sends the signal to processor that presenttask is finished now and so anothertask can be performed. XMOS<sup>®</sup> used 'chan' keyword as shown in figure 7 (c) [27]. Sometimes microcontroller can be ina busy state, at that time user has to wait for some time. XMOS<sup>®</sup> time stamping explain in figure 7 (d) [27] in which after the 100 time units led will be high and after the wait for 100 time unit led will on low stage.

Figure 7. Time critical analysis and multitasking using XMOS® startKIT

#### **3. EXPERIMENTAL RESULTS**

Experimental results mentioned in this section is based on time critical analysis of sequential and parallel task on multi core microcontroller XMOS® and the multicore microprocessor i3 and i5.

#### 3.1. Time critical analysis of sequential and parallel tasks on multicore microprocessor

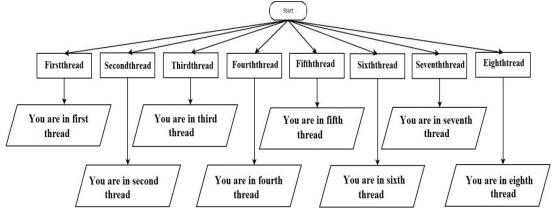

Analysis of the sequential and parallel [28] behaviors are observed that there is a huge difference in their execution time. Multithread program [29] in c executed using POSIX and the thread level parallelism (TLP) is shown in figure 8. First, it is triedwith two threads then four and eight threads are used and shown in figure 8 which is just giving the status of the tread. The results are checked with the help of profiling, which is obtained at the table5. The same process is applied to a different machine.

Figure 8. Flow chart of thread level parallelism

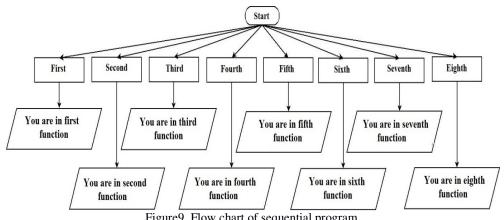

Nothe same thingng is done by simple sequential c code as shown in figure 9 and obtain the sequential table as illustrated in table 6 afteanalyzingng the each function execution time as well aprogramme execution time. The same analysis done with various otherarchitectures [30] and the difference in their execution time and the cache misses by the processor are examined First program load in the cache then it will be executed. If any variable's value or any instruction is not available in cache [31] then processor first fetches the instruction which takes some time that is called cache misses.

Figure9. Flow chart of sequential program

| Architecture | Compiler | No of Threads | Compile time(sec)                          | Exc. time of each function(sec)                                                                                                                                        | Cache Misses (%)                                                                           |

|--------------|----------|---------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Intel i3     | Gcc      | 2             | real =5.002<br>user =9.976<br>sys =0.022   | Firstthread = 5.64<br>Secondthread =4.44                                                                                                                               | I1 Misses =0.48<br>D1 Misses =1.1<br>LLi Misses =0.29<br>LLd Misses =0.6<br>LL Misses =0.3 |

| Intel i5     | Gcc      | 2             | real =5.002<br>user =5.580<br>sys =0.003   | Firstthread = 1.18<br>Secondthread =0.21                                                                                                                               | I1 Misses =0.46<br>D1 Misses =1.1<br>LLi Misses =0.25<br>LLd Misses =0.6<br>LL Misses =0.3 |

| Intel i3     | Gcc      | 4             | real =5.002<br>user =18.481<br>sys =0.0721 | Firstthread =4.57<br>Secondthread =3.54<br>Thirdthread =2.42<br>Fourththread =2.04                                                                                     | I1 Misses =0.49<br>D1 Misses =1.1<br>LLi Misses =0.25<br>LLd Misses =0.6<br>LL Misses =0.3 |

| Intel i5     | Gcc      | 4             | real =5.002<br>user =16.712<br>sys =0.004  | Firstthread =1.28<br>Secondthread =1.21<br>Thirdthread =1.06<br>Fourththread =0.95                                                                                     | I1 Misses =0.48<br>D1 Misses =1.1<br>LLi Misses =0.20<br>LLd Misses =0.6<br>LL Misses =0.3 |

| Intel i3     | Gcc      | 8             | real =5.003<br>user =21.538<br>sys =0.052  | Firstthread = 1.25<br>Secondthread =1.11<br>Thirdthread =1.03<br>Fourththread =0.79<br>Fifththread=0.67<br>Sixththread=0.50<br>Sevenththread=0.22<br>Eighththread=0.11 | I1 Misses =0.50<br>D1 Misses =1.1<br>LLi Misses =0.25<br>LLd Misses =0.6<br>LL Misses =0.3 |

| Intel i5     | Gcc      | 8             | real =5.003<br>user =19.948<br>sys =0.004  | Firstthread = 2.70<br>Secondthread =1.29<br>Thirdthread =0.19<br>Fourththread =0.64<br>Fifththread=0.64<br>Sixththread=0.73<br>Sevenththread=0.65<br>Eighththread=0.18 | I1 Misses =0.49<br>D1 Misses =1.1<br>LLi Misses =0.24<br>LLd Misses =0.6<br>LL Misses =0.3 |

#### Table 5 Multi-thread Profiling

| Architecture | Compiler | No of<br>Functions | Compile time(sec) | Exc. time of<br>each<br>function(sec) | Cache Misses (%) |

|--------------|----------|--------------------|-------------------|---------------------------------------|------------------|

| Intel i3     | Gcc      | 2                  | real =30.528      | First = 15.40                         | I1 Misses =0.49  |

|              |          |                    | user =30.480      | Second =15.41                         | D1 Misses =1.1   |

|              |          |                    | sys =0.044        |                                       | LLi Misses =0.25 |

|              |          |                    |                   |                                       | LLd Misses =0.6  |

|              |          |                    |                   |                                       | LL Misses =0.3   |

| Intel i5     | Gcc      | 2                  | real =18.579      | First = 9.14                          | I1 Misses =0.48  |

|              |          |                    | user =18.580      | Second =9.13                          | D1 Misses =1.1   |

|              |          |                    | sys =0.008        |                                       | LLi Misses =0.25 |

|              |          |                    |                   |                                       | LLd Misses =0.6  |

|              |          |                    |                   |                                       | LL Misses =0.3   |

| Intel i3     | Gcc      | 4                  | real =1m0.987     | First = 15.39                         | I1 Misses =0.48  |

|              |          |                    | user =1m0.911     | Second =15.41                         | D1 Misses =1.1   |

|              |          |                    | sys =0m0.068      | Third =15.40                          | LLi Misses =0.25 |

|              |          |                    |                   | Fourth =15.30                         | LLd Misses =0.6  |

|              |          |                    |                   |                                       | LL Misses =0.3   |

| Intel i5     | Gcc      | 4                  | real =37.332      | First = 9.47                          | I1 Misses =0.46  |

|              |          |                    | user =37.340      | Second =9.28                          | D1 Misses =1.1   |

|              |          |                    | sys =0.016        | Third =9.22                           | LLi Misses =0.25 |

|              |          |                    |                   | Fourth =9.22                          | LLd Misses =0.6  |

|              |          |                    |                   |                                       | LL Misses =0.3   |

| Intel i3     | Gcc      | 8                  | real =2m2.215     | First = 15.39                         | I1 Misses =0.48  |

|              |          |                    | user =2m2.030     | Second =15.34                         | D1 Misses =1.1   |

|              |          |                    | sys =0m0.160      | Third =15.32                          | LLi Misses =0.25 |

|              |          |                    |                   | Fourth =15.31                         | LLd Misses =0.6  |

|              |          |                    |                   | Fifth=15.34                           | LL Misses =0.3   |

|              |          |                    |                   | Sixth=15.32                           |                  |

|              |          |                    |                   | Seventh=15.34                         |                  |

|              |          |                    |                   | Eighth=15.32                          |                  |

| Intel i5     | Gcc      | 8                  | real =1m13.649    | First = 9.27                          | I1 Misses =0.48  |

|              |          |                    | user =1m13.692    | Second =9.27                          | D1 Misses =1.1   |

|              |          |                    | sys =0.024        | Third =9.26                           | LLi Misses =0.25 |

|              |          |                    |                   | Fourth =9.26                          | LLd Misses =0.6  |

|              |          |                    |                   | Fifth=9.25                            | LL Misses =0.3   |

|              |          |                    |                   | Sixth=9.24                            |                  |

|              |          |                    |                   | Seventh=9.22                          |                  |

|              |          |                    |                   | Eighth=9.13                           |                  |

| Table6. | Sequential | Profiling | Table |

|---------|------------|-----------|-------|

|---------|------------|-----------|-------|

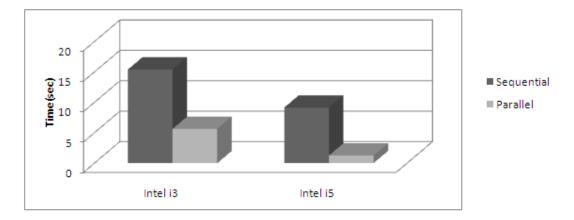

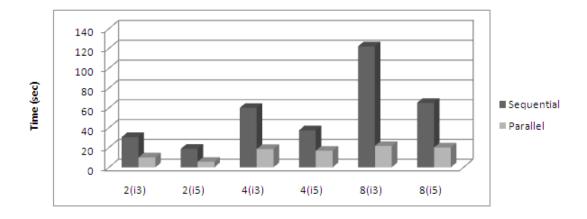

Various architectures used different frequency which affects the execution time. The experimental results mentioned in table 5 and table 6 explain how function execution time varies with architecture which is illustrated in figure 10. Not only the architecture but also the number of threads [32] is important the execution time of a machine. In parallelcomputation all the CPUs are treated as individual entity which are connected to each other for better communication and it executes all the threads at the same time, which could be proven with the help of figure 11, it could also be observed with the same diagram that every function has a different time boundation that is also known as time bounded computation. The execution speed of Intel<sup>®</sup> i3 to Intel<sup>®</sup> [33] i5

reduces as the frequency of the device increases its results are illustrated in table 6. Aftercomparing the results mentioned in tables 5 and 9 the conclusion is that the good amount of possibility that multicore arc. For controllers are very effective and efficient for time critical execution.

Figure 10 shows the execution time depends upon the architecture also. As Intel<sup>®</sup> i5 has higher frequency [34] than Intel<sup>®</sup> i3 and also Intel<sup>®</sup> i3 has only 2 cores (dual core) and Intel<sup>®</sup> i5 has four courses. Intel<sup>®</sup> i5 has less execution time in comparison to Intel<sup>®</sup> i3. Execution time reduces as the frequency and number of core increases. Even applying the same code for different-2 processors, then also we get different-2 time. As it is noticed that in every caseexecution time is less in parallel of Intel<sup>®</sup> i5 than Intel<sup>®</sup> i3 (which has number of cores) as shown in figure 11 that's proves requirement of multi-core and parallel processing is increasing rapidly.

Figure10. Function Execution time

Figure 11. Total execution time

Although same program is used for sequential as well as the parallel processing, but in the parallel processing Intel<sup>®</sup> i3 takes almost 5 sec and Intel<sup>®</sup> i5 takes 2 sec and in case of sequential program Intel<sup>®</sup> i3 takes 15 sec and Intel<sup>®</sup> i5 takes 9 sec which is shown in figure10. The total execution time [35] depends upon the architecture and the number of threads or function used by the program. As the number of threads and function increases, total execution time of the processor increases as we used same threads and the same program. Using <sup>®</sup>i3 with 2 functions in a parallel program is given worst execution time, whereas in Intel<sup>®</sup> i5 with same 2 functions in parallel processing [36] gives best result as illustrated in figure 11.

## **3.2.** Time Critical analysis of sequential and parallel task on Multi core microcontroller

Results show that the development of parallel program by xtime composer for SK131552, the task mentioned in the core has the special property of activating and setting a specific character using 3x3 led matrix which is communicating through inbuilt com port i.e. 32 which is 20 bits long. The 1st bit from first led & 2nd bit from second led & 3rd bit assign to third led. 8th bit, 9th, 10th, 11th, 12th, 13th bit assigns to fourth, fifth, sixth, seventh, eighth & ninth led respectively, Others are don't care. The words like 'Y' 'O' 'U' 'K' is as shown in figure 12(a)-(d).

Figure 12(a). Display Y 3\*3 LED

Figure 12(b). Display O 3\*3 LED

Figure 12(c). Display U 3\*3 LED

Figure 12(d). Display K 3\*3 LED

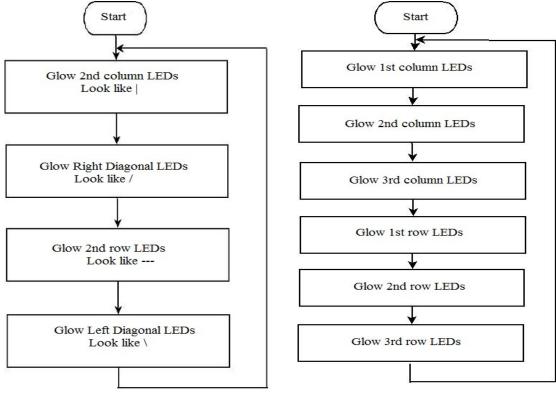

The sequential flow chart of spinning ball is shown in Figure 13 in which 3x3 led glows and rotate in a circle.Figure 14 shows the flow chart of a pattern shift in which LEDs of the first column, then second, then third column, then first, second then third row glows and are repeated again in the same manner.

International Journal of Embedded systems and Applications(IJESA) Vol.5, No.1, March 2015

Figure 13. Sequential execution of spinning ball program

Figure 14. Sequential execution of pattern formation program

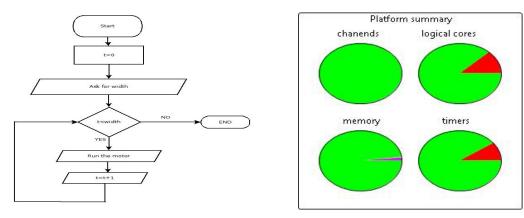

Parallelization is demonstrated using the servo motor. Flow chart of Servo motor control is shown in figure 15 using xTOOLS [27] the obtained result is shown in figure 16. The platform summary shows the how many cores, timer, memory and channel used by the program. It also displays the value of timer and how much memory occupied by the program. startKIT [27] has 8 logical cores, 32 channels, 655036 bites memory space and 10 timer. Table 7 illustrates how many of them are occupied by this program.

Figure 15. Flow chart of servo motor control

Figure16. Analysis

| Name          | Used          | Free             |

|---------------|---------------|------------------|

| Chanends      | 0%            | 100%             |

| Logical Cores | 1(12.5%)      | 7(97.5%)         |

| Memory        | 336bit(0.51%) | 65200bit(99.49%) |

| Timer         | 1(10%)        | 9(90%)           |

Table 7. Result of servo motor control

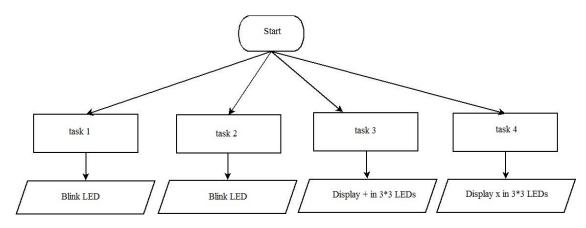

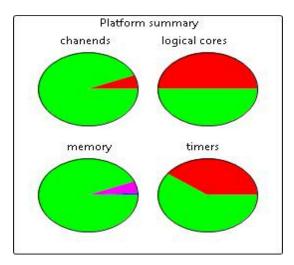

Multitasking [36] is also performed in this which 4 tasks perform simultaneously as shown in figure 17, with the help of 'par' keyword. First two cores are assigned to blink the two additional led and third core is assigned to display '+' and fourth core is used to display 'X' in 3x3 led. Third and fourth core work on same 3x3 led so it required channel by using 'chan' keyword to assign the task so that both cannot overlap also profiling is done using gproof and noted that how much time is taken by all the functions and result [37] is shown in table 8 and its profiling graph is illustrated in figure 18. How much memory, channels, logical cores and timer used by this program is illustrated in table 9. In this program stack is also used so memory is occupied by stacking as well as program.

Figure17. Flow chart of multitasking

| Function Name | Time            |

|---------------|-----------------|

| task1         | 125ns           |

| task2         | 152ns           |

| task3         | 2.548 micro sec |

| task4         | 3.45 micro sec  |

Table 8. Execution time of each thread

| Name            | Used        | Free          |

|-----------------|-------------|---------------|

| Chanends        | 3(9.38%)    | 29(90.63%)    |

| Logical Cores   | 4(50%)      | 4(50%)        |

| Memory(Stack)   | 604(0.92%)  | 60812(92.79%) |

| Memory(Program) | 4120(6.29%) |               |

| Timers          | 4(40%)      | 6(60%)        |

#### Table 9. Result of multitasking

From the experimental results we can illustrate that the time taken by the sequential programming on multicore[38] microcontroller is in 'micro seconds' whereas time [39] taken by the multicore microprocessor is in 'seconds' and 'minutes' which proves that the sequential task on microcontroller can be done faster than the microprocessor. Similarly, the time taken for task parallelization on multicore [40] microcontroller is in 'nanoseconds' whereas multicore microprocessor takes 'seconds' which again proves that the parallel task on microcontroller can be done faster than the microprocessor.

#### **4.** CONCLUSIONS

It can be seen that the time critical analysis on micro controller, task parallelization for complex programming structures can be compiled in less time, although it has been observed that these techniques of programming are easy for an advanced developer but tough for a new or the beginners. Using above mentioned results user easily analyze the performance of multicore microcontroller. The task Parallelization for multicore controller is still a challenge due to its complex programming structure, but it gives high versatility and reliability to perform real-time operations. The Future focus of the research is to implement it in automation control system using SPI and I2C interfaces. In this research every thread is assigned by the controller to its different cores by itself, future goal will concentrate by hand on assignment of threads on the cores. Also in this paper time critical analysis results and examples are restricted only for basic applications. Future work will be focused on expansion of present experimentations on time critical analysis on real time applications and embedded system.

#### **ACKNOWLEDGEMENTS**

The authors would like to thank to Dr. Abhishek Sharma for their guidance and constant supervision as well as for providing necessary information regarding the project & also for their support in completing the project. The authors would like to express gratitude towards parents &

member of LNMIIT for their kind co-operation and encouragement which help in completion of this project. Thanks and appreciations also go to the Texas instrumental Lab.

#### REFERENCES

- Flores A., Aragon, Acacio, "Sim-PowerCMP: A detailed Simulator for Energy Consumption Analysis in Future Embedded CMP Architecture", pp 752-757, AINAW-21st International Conference IEEE, 2007.

- [2] Balaji Venu, "Multi-Core Processors-An Overview", pp: 1-6, Cornell University Library, 2011.

- [3] David E. Culler, Jaswinder Pal Singh and Anoop Gupta, Parallel Computing Architecture. San Francisco, CA: Morgan Kaunfmann, 1999.

- [4] Jiang-Yi Shi, "Optimization of Shared Memory Controller for Multi-core System", pp 287-289, ICSICT-10th IEEE International Conference, 2010.

- [5] M. Sasikumar, Dinesh Shikhare and P. Ravi Praskash(2000), "Parallel processing Architecture" in Introduction to Parallel Processing,9th Ed, India, Eastern Economy Edition, 2006, ch 2, pp 19-37.

- [6] Georg Haner and Gerhard Wellein," Basics of Parallelization" in Introduction to High Performance Computing for Computing for Scientifics and Engineers, 1 Ed. Boca Raton, FL: CRC Press, 2011,ch 5, pp 115-140.

- [7] Tao Cui, Franchetti, "Optimized Parallel Distribution Load Flow Solver on Commodity Multi-Core CPU", pp 1-6, IEEE, 2012.

- [8] Koen De Bosschere, Wayne Luk, Xavier Martorell, Nacho Navarro, Mike O'Boyle, Dionisios Pnevmatikatos, Alex Ramirez, Pascal Sainrat, Andrew Seznec, Per Stenstr¨om, and Olivier Temam, "High-Performance Embedded Architecture and Compilation Roadmap", pp.5-29, HiPEAC I, LNCS 4050, 2007.

- [9] Kushal Datta, Arindam Mukherjee, Guangyi Cao, Rohith Tenneti, Vinay Vijendra Kumar Lakshmi, Arun Ravindran and Bharat S. Joshi, "CASPER: Embedding Power Estimation and Hardware-Controlled Power Management in a Cycle-Accurate Micro Architecture Simulation Platform for Many-Core Multi-Threading Hetregeneous Processors", JLPEA,2(1), pp 30-68, 2012.

- [10] Wei Tong, Moreira O., Nas R., Van Berkel K., "Hard-Real-Time Scheduling on a Weakly Programmable Multi-core Processor with Application to Multi-standard Channel Decoding", pp 151-160, RTAS-IEEE 18th, 2012.

- [11] Georgios Kornaros, "Multi-core Architectures for Embedded Systems" in Multi-Core Embedded System, 1st Ed, Boca Raton, FL: Taylor & Francis Groups, 2010, ch 1,pp 1-27.

- [12] Goehringer, Chemaou, Huebner, "Invited paper: On-chip Monitoring for Adaptive Heterogeneous Multicore System", pp 1-7, ReCoSoC 7th IEEE International Workshop, 2012.

- [13] Mekelle and Ethiopia, "Concurrent Approach to Flynn's SPMD Classification", pp 79-81, IJCSIS, 2010

- [14] Shameem Akhter and Jason Roberts, Multi-Core Programming. Richard Bowles, US: Intel press, 2006.

- [15] Gepner, Kowalik, "Multi-Core Processors: New Way to Achieve High System Performance", pp 9-13, International symposium on parallel computing in electrical engineering, IEEE, 2006.

- [16] J. Kahle, "The IBM Power4 Processor,"Microprocessor Forum presentation reported in: K. Diefendorff, "Power4 Focuses on Memory Bandwidth", pp. 11-17, Microprocessor Report, Oct. 6, 1999.

- [17] J.M. Tendler et al., "Power4 System Microarchitecture", pp. 5-26, IBM J. Research and Development, vol. 46, no. 1, Jan. 2002.

- [18] Peter Pacheco, "Shared-Memory Programming with pthread" in An Introduction to Parallel Programming, 1 Ed. Burlington, MA: Morgan Kaufma, 2011, ch 4, pp 151-208.

- [19] Mark D. Hill, Michael R. Marty, "Amdahl's Law in the Multicore Era", pp 33-38, IEEE Computer Society, 2008.

- [20] Pornsoongsong W., Chongstitvatana P."A Parallel Compiler for Multi-core Microcontrollers", pp 373-377,DICTAP-2nd International Conference IEEE, 2012.

- [21] startKITHardwareManual[Online].Available:https://www.xmos.com/support/xkits?subcategory=Starter%20Kits&product=17441&secure=1,Febrerury 25th, 2013.

- [22] "xCORE Multicore Microcontroller", XMos, 16th sep, 2013.

- [23] "Next-Generation XTIMEcomposer Studio Makes Developing Multicore code easy" Internet: http://eecatalog.com/multicore/2013/07/18/next-generation-xtimecomposer-studio-makes-developingmulticore-code-easy/, July 18th, 2013 [October 16th, 2014].

- [24] "XMOS XTA TIMING ANALYZER", XMos whitepaper, 8thMay 2013.

- [25] "XSCOPE Library API", XMos, November 12th, 2013.

- [26] XMOSProgrammingGuide[Online].Available:https://www.xmos.com/support/xkits?subcategory=Starter%20Kits&product=17441&component=17653, October 9th, 2014[November 6th 2014].

- [27] startKITTutorial[Online].Available:https://www.xmos.com/support/xkits?subcategory=Starter%20Kits&product=17441&component=17263, November 20th, 2013[October 12th, 2014].

- [28] Simon Marlow, "Parallel Programing Using Thread" in Parallel and Concurrent Programming in Haskell, 1st Ed. Sebastopol, CA:O'Reilly, 2013, pp 225-240.

- [29] Stephen W. Keckler, Kunle Olukotun and H. Peter Hofstee(2009),"Speculatively Multithreaded Architectures" in Multicore Processors and System, Springer, New York, 2009, ch 4, pp 111-140.

- [30] Anders Pettersson, Henrik Thane, "Testing of MultiTasking Real-Time System with Critical Sections", pp 578-594, RTCSA, 2004.

- [31] Vipin S. Bhure, Praveen R. Chakole, "Design of Cache Controller for Multi-core Processor System", pp 167-173, IJECSE, ISSN: 2277-1956, IJECSE, 2012.

- [32] Caprita, H.V., Popa M., "Design Methord of Multithreaded Architectures for Multicore Microcontrollers", pp 427-432, SACI-6th IEEE international Symposium, 2011.

- [33] Stephen Blair-Chappel and Andrew Stokes, "Nine tips to parallel programming heaven" in Parallel Programming with Intel Parallel Studio XE, 1stEd, Indianapolis, IN: John Wiley & Sons, 2012, ch 14,sec 3, pp 397-410.

- [34] Spyros Blanas, Yinan Li, Jignesh M. Patel, "Design and Evaluation of Many Memory Hash Joint Algorithms for Multi-Core CPUs", pp 37-48, SIGMOD, 2011.

- [35] N. Ramasubramanian, Srinivas V.V., Chaitanya V., "Studies on Performance Aspect of Scheduling Algorithms on Multicore Platform", IJARCCSE, vol. 2, issue 2, 2012.

- [36] Blake, Dreslinski, Mudge, "A Survey of Multicore Processors", pp 26-37, Signal Processing Magazine IEEE, 2009.

- [37] Jiang-Yi Shi, Ai-Nv An, Kang Li, Hao, Yue, Pei-Yan Liu, Ying Kang, "Optimization of Shared Memory Controller for Multi-Core System", pp 287-289,ICSICT-10th IEEE international conference, 2010.

- [38] Jun Xu, Yongxin Zhu, Jiang L., Junjie Ni, Kai Zheng, "A Simulation for Multi-Core Processor Micro-Architecture Featuring Inter-Core Communication, Power and Thermal Behavior", pp237-242, ICESS Symposia IEEE, 2008.

- [39] Gerassimos Barlas, "Time measurement", Multicore and GPU Programming, 1st Ed Waltham, MA: Morgan Kaufmann, 2015, APP. C,pp 635-638.

- [40] Reinaldo Bergamaschi, Indira Nair, Gero Dittmann, Hiren Patel, Geert Janssen, Nagu Dhanwada, Alper Buyuktosunoglu, Emrah Acar, Gi-Joon Nam, Guoling Han, Dorothy Kucar, Pradip Bose, John Darringer, "Performance Modeling for Early Analysis of Multi-Core System", pp 209-214, Code+ISSS Proceedings of the 5th IEEE, 2007.

#### AUTHORS

**Prerna Saini** is pursuing B. Tech in the branch Electronics and Communication Engineering at the LNM Institute of Information Technology, Jaipur (Rajasthan), India. Her area of interests is embedded System, Multicore Microcontroller and Microprocessor and High Performance Computing.

**Ankit Bansal** is pursuing B. Tech in the branch Electronics and Communication Engineering at GLA University, Mathura (U.P), India. His current interests are in Embedded System, Multicore Microcontroller and Microprocessor and cloud computing.

**Abhishek Sharma** obtained his B. Tech degree in ECE from Jiwaji University, Gwalior, India. He worked with two Telecom Companies i.e. ZTE and Huawei. After he worked in CNR, Milan as Research Engineer. He finished his Ph. D in multicore and many core systems in 2010 from university of Genoa, Italy. He is currently working as Assistant Professor in the Dept. of ECE in LNMIIT, Jaipur (Rajasthan), India. His current research interest includes high performance embedded system, many cores and multicore architecture.