# DESIGN AND SIMULATION OF CMOS OTA WITH 1.0 V, 55db GAIN & 5PF LOAD

Dhaval Modi<sup>1</sup> and Jayesh Patel<sup>2</sup> <sup>1</sup>Department of Electronics & Communication Engineering, G.P. PALANPUR, Gujarat, India

<sup>2</sup>Department of Electronics & Communication Engineering, G.P. PALANPUR, Gujarat, India

#### **ABSTRACT**

Design of very large scale analog integrated circuit (analog VLSI) is very much complex and requires much compromising nature to achieve application specific objective. With maximizing the efforts to reduce power consumption and to reduce W/L ratio, the analog integrated circuit industry is constantly developing smaller power supplies. Now days, challenges of analog integrated circuit designer are to make block of small power supplies with little or no reduction in performance. The CMOS OTA is designed in 25.5nm CMOS technology with 1.0V power supply to observe the configurations. In design of CMOS OTA TANNER EDA TOOL is used. Coding and simulation is done in T-Spice and layout is prepared in L-Edit. D.C analysis, A.C analysis, slew rate and analysis of transient response have been done in T-Spice. Waveforms are observed in W-Edit.

## **Keywords**

DRC, Net list, Slew Rate, Transconductance Amplifier

## **1. INTRODUCTION**

The importance of analog circuits using low supply voltage is enormously increasing in last decades. Especially large component densities demands lower power consumption <sup>[2]</sup>. The power consumption can be minimized either by reducing the supply voltage or gate oxide thickness (Tox). If Tox is reduced, tolerance of the CMOS device for high gate voltage is also reduced. Therefore reasonable method for minimizing power consumption is to reduce power supply.

CMOS elements are useful building blocks for the design of many analog and analog-digital signal processing systems. Two important characteristics of CMOS devices are high noise immunity and low static power consumption. Because of these characteristics, the vast majority of modern integrated circuit manufacturing is on CMOS processes.

Operational Transconductance Amplifiers are important building block in many analog systems. These analog systems often require low power, fast settling time and high dynamic range. The CMOS Operational Transconductance Amplifier (OTA) is a unique device with characteristics particularly suited to applications viz. multiplexing, amplitude modulation, analog multiplication, gain control, switching circuitry and comparators.

# 2. DESIGN OF OTA

## 2.1. Low voltage and low power amplifier design

In low-voltage design, the main consideration is to maintain the output swing as higher as possible. This can be achieved when no cascading transistors can be used in the output stage. For minimum power consumption, the number of current branches should be minimized. So the current mirror amplifier is best suited for low-power low-voltage amplifier<sup>[1]</sup>.

## 2.2. Current Mirror Amplifier

The circuit in which output current is forced to equal the input current is said to be a current mirror circuit. It is special case of constant current bias. An advantage of current mirror circuits is that it takes fewer components, simple to design and easy to fabricate.

#### 2.3. Parameter require for designing CMOS OTA

- 1) Slew rate

- 2) Common-mode input range (ICMR)

- 3) Common-mode rejection ratio (CMRR)

- 4) Power supply rejection ratio (PSRR)

- 5) Voltage Gain

#### 2.4. Design Specification

$V_{dd}$  = - $V_{ss}$  = 1.0 V, SR  $\ge$  10V/µs, CL=5pF, a small signal differential voltage gain of 55db, -1.5 $\le$  ICMR  $\le$  2V and Pdiss  $\le$  1mW

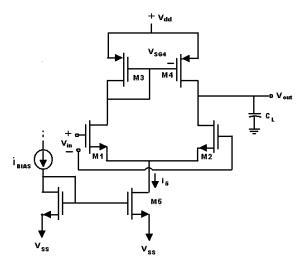

Figure 1. Design of CMOS OTA

### 2.5 MATLAB Code for extraction of designing parameter

Vdd = input ('enter the value of Vdd = '); SR = input ('enter the value of slew rate SR =');

CL = input ('enter the value of slew rate CL=');

$I_5 = SR*CL$ Pdiss = input ('enter the value of power diss. Pdiss');  $V_{ss} = input$  ('enter the value of  $V_{ss} = -V_{dd} =$ '); ..... .....  $Y_n = input$  ('enter the value of  $Y_n =$ ');  $Y_p = input (enter the value of <math>Y_p = );$ ..... Rout =  $2/((Y_n + Y_p)*I5);$ Vin = input ('enter the value of Vin = '); .....  $V_{sg3} = V_{dd} - V_{in} + V_{tn}$  $K_p = input$  ('enter the value of  $K_p = '$ );  $K_n = input$  ('enter the value of  $K_n = '$ );  $W_3/L_3 = I_5 / (K_p * (V_{sg3} - 0.7) * (V_{sg3} - 0.7))$ Av = input ('enter the value of Av =');  $W_1/L_1 = ((Av)^2 (Y_n+Y_p)^2 I_5/2)/(2*K_n);$  $V_{gs} = sqrt((I_5/K_n * W_1/L_1)) + 0.7;$ Vds5 = Vin-Vss-Vgs; $W_5/L_5 = sqrt((2*I_5)/K_n*(V_{ds}5)^2);$

## **3.** LAYOUT AND VERIFICATION CONSIDERATION

Layout should be verified with design rule viz. Design Rule Check (DRC) and Layout Versus Schematic (LVS).

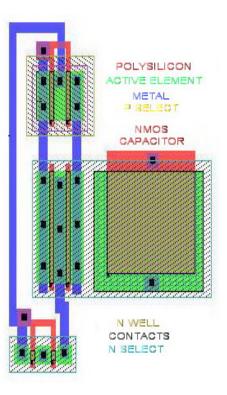

Figure 2. Layout of CMOS OTA in 25.5nm

## 3.1 Layout Versus Schematic (LVS) Summary (Extracted code from layout)

2 1 C=5.0147962p \* C7 PLUS MINUS (49.5 -45 91 -11.5)

M6 5 3 4 11 NMOS L=2n W= 56n AD=45.25p PD=28n AS=21p PS=14n \* M6 DRAIN GATE SOURCE BULK (23 -73.5 25 -70.5) M5 4 3 3 11 NMOS L=2n W=56n AD=21p PD=14n AS=45.25p PS=28n \* M5 DRAIN GATE SOURCE BULK (13 -73.5 15 -70.5) M4 6 10 5 11 NMOS L=2n W=58n AD=222p PD=86n AS=111p PS=43n \* M4 DRAIN GATE SOURCE BULK (30 -48.5 32 -11.5) M3 5 9 7 11 NMOS L=2n W=58n AD=111p PD=43n AS=222p PS=86n \* M3 DRAIN GATE SOURCE BULK (22 -48.5 24 -11.5) M2 3 7 7 8 PMOS L=2n W=51n AD=48p PD=22n AS=96p PS=44n \* M2 DRAIN GATE SOURCE BULK (22 5 24 21) M1 6 7 3 8 PMOS L=2n W=51n AD=96p PD=44n AS=48p PS=22n \* M1 DRAIN GATE SOURCE BULK (30 5 32 21)

\* Total Nodes: 11

\* Total Elements: 7

Sr.No

1

2

3

4

5

6

\* Total Number of Shorted Elements not written to the SPICE file: 0

$W_2/L_2$

$W_3/L_3$

$W_4/L_4$

W5/L5

W6/L6

\* Extract Elapsed Time: 0 seconds

.END

| Transistor<br>Variable | W(n) | L(n) | W/L ratio |

|------------------------|------|------|-----------|

| $W_1/L_1$              | 51   | 2    | 25.5      |

51

58

58

56

56

2

2

2

2

2

25.5

29

29

28

28

## **4. SIMULATION RESULT**

## 4.1. Simulation in T-spice

T-Spice Pro is part of a complete integrated circuit design tool suite for layout, verification and simulation offered by Tanner EDA.

1) T-Spice: Analog / digital circuit simulator

2) W-Edit: Waveform viewer

AC Analysis

Perform AC analysis to characterize the circuit's dependence on small-signal input frequency.

.ac {linloctldec} num start stop [sweep info] [analysis name=name] DC Analysis

Perform DC transfer analysis to study the voltage or current at one set of points in a circuit as a function of the voltage or current at another set of points.

.dc info [sweep] info [sweep] info

## 4.2. Different Types of Simulation

## 4.2.1. DC characteristic

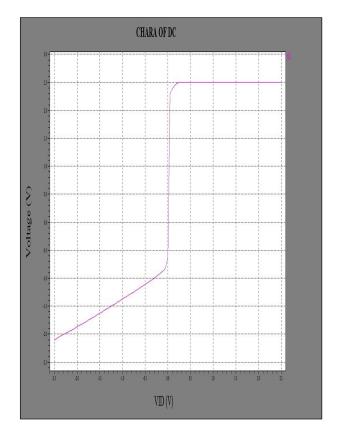

.DC VID -2.5V 2.5V 0.5V .TF V(5) VID .PRINT DC V(5) .END

Figure 3. DC Characteristic of CMOS OTA

## 4.2.2. Slew Rate

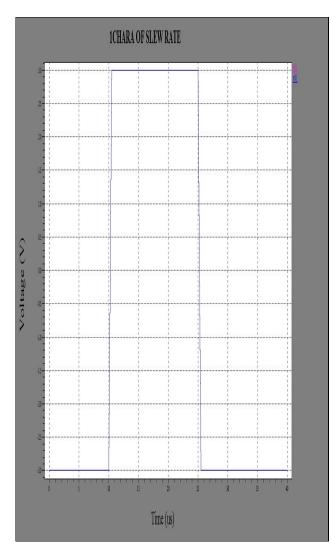

VIN2 1 0 PWL (0,-3V 10US,-3V 10.505US, 3V 25US, 3V 25.505US,-3V 1S,-3V) VIN1 2 0 PWL (0,-3V 10US,-3V 10.505US, 3V 25US, 3V 25.505US,-3V 1S,-3V) .TRAN .1NS 40US .PRINT V (5) V (1) .PROBE .END From waveform of slew rate = (10-(-10))/.5µs = 40 V/µs

International Journal of Managing Public Sector Information and Communication Technologies (IJMPICT) Vol. 5, No. 2, June 2014

Figure 4. Slew Rate Analysis

# 4.2.3. AC characteristic

.AC DEC 5 0.1HZ 1MegHZ .TF V(5) VID .PRINT AC V(5) VP(5) VID .PROBE

International Journal of Managing Public Sector Information and Communication Technologies (IJMPICT) Vol. 5, No. 2, June 2014

Figure 5. AC Characteristic of CMOS OTA

## **5.** FUTURE WORK

The OTA layout con be further optimized to take up less space and also to get better symmetry. We will make layout of viz. Telescopic, Folded-Cascode and Two-stage CMOS OTA. We will compare their characteristics like gain, Speed, Power, Noise and Swing<sup>[1]</sup>.

## **6.** APPLICATIONS

## **IC CA3080A**

IC CA3080A is especially suited for many low frequencies, low-power four-quadrant multiplier applications. The basic multiplier circuit is particularly useful for waveform generation, double balanced modulation, and other signal processing applications, where low-power consumption is essential and accuracy requirements are moderate. We can make the astable multi vibrator, monostable multi vibrator and peak detector <sup>[11].</sup>

## **IC OPA2662**

It is dual, wide band Operational Transconductance Amplifier. The OPA2662 is a versatile driver device for ultra wide-band systems, including high-resolution video, RF and IF circuitry, communications and test equipment<sup>[11]</sup>.

CMOS OTA is used in following application like,

- 1) LED and LASER diode driver

- 2) High current video buffer or line driver

- 3) RF output stage driver

- 4) High density disk drives

## **7.** CONCLUSION

Simulations show the output is reliable up to about 10MHz, which is sufficient to find the 3dB bandwidth of the OTA. Structure of CMOS OTA is simple and is used as compare to ordinary op-amp because its output is a current. We can retrieve information about gain margin and phase margin. According to that we can retrieve information about pole and stability of the design.

## ACKNOWLEDGEMENT

Author would like to thanks his head of electronics and communication department for providing facilities and co-author for their continuous support, help and encouragement for this research work.

#### REFERENCES

- [1] CMOS Analog Circuit Design By Phillip E. Allen and Doiglas R. Holberg

- [2] Design of Fully Different CMOS Amplifier For Cliping Amplifier By Behnam Karmani

- [3] Operational Transcondunce Amplifier By WikiSource

- [4] S.S. Rajput and S.S. Jamuar, "Low Voltage Analog Circuit Design Techniques," IEEE Circuits and Systems Magazine, vol. 2, no. 1, pp. 24-42, First Quarter, 2002.

- [5] M. Steyaert, V. Peluso, J. Bastos, P. Kinget, W. Sansen, K. U. Leuven, "Custom Analog Low Power Design: The Problem of Low Voltage and Mismatch," IEEE 1997 Custom Integrated Circuits Conference, pp. 285-292.

- [6] S. Chatterjee, Y. Tsivides, P. Kinget, "0.5-V Analog Circuit Techniques and Their Application in OTA and Filter Design," IEEE Journal of Solid-State Circuits, vol. 40, no. 12, pp. 2373-2387, December 2005.

- [7] S. Chatterjee, Y. Tsivides, P. Kinget, "A 0.5-V Bulk-Input Fully Differential Operational Transconductance Amplifier,"

- [8] Shankar, J. Silva-Martinez, E. Sanchez-Sinencio, "A Low Voltage Operational Transconductance Amplifier using Common Mode Feedforward for High Frequency Switched Capacitor Circuits," IEEE International Symposium on Circuits and Systems, Vol. 1, pp. 643-646, May 2001

- [9] N. Mohieldin, E. Sanchez-Sinencio, J. Silva-Martinex, "A Fully Balanced Pseudo-Differential OTA with Common-Mode Feedforward and Inherent Common-Mode Feedback Detector," IEEE Journal of Solid-State Circuits, vol. 38, no. 4, April 2003

- [10] Shouli Yan and Edgar Sanchez-Sinencio, "Low Voltage Analog Circuit Design Techniques: A Tutorial," IEICE Transactions on Analog Integrated Circuits and Systems, vol. E00-A, no. 2, February, 2000

- [11] Datasheet of IC CA3080A and OPA 2662

#### Authors

Dhaval Modi received the B.Tech degree in electronics and Communication engineering from Nirma University, Ahmedabad, India in 2009 and M.E. degree in Communication System Engineering from L.D. College of Engineering, Gujarat, India in 2011. His area of research includes analog VLSI and making various applications using different algorithms.

Jayesh Patel received the B.E. degree in electronics and Communication engineering from Gujarat University, Ahmedabad, India in 2006 and M.E. degree in Communication System Engineering from L.D. College of Engineering, Gujarat, India in 2009. Currently he is working with technical education board, Gandhinagar, Gujarat since 2011.