# A 60 GHz Analog Phase Shifter in 65 nm Bulk CMOS Process

ETB.Samuel Jigme Harrison and Zhang Yue Ping

Department of Electrical and Electronic Engineering, Nanyang Technological University, Singapore - 639798 EDWI0009@ntu.edu.sg eypzhang@ntu.edu.sg

#### ABSTRACT

A 60 GHz Analog Phase Shifter in 65nm bulk CMOS process has been explored for microwave frequency applications. It is an analog phase shifter with three transistors in the form of an active circulator and a LC network to attain the desired phase shift. This phase shifter is designed to work at a high frequency of 60 GHz to attain phase shift range of 140°. The proposed phase shifter works at supply voltage lower than 2.5 V. The phase shifter exhibits low insertion loss of 3.73 dB and low power consumption which is a challenging result for circuits working in microwave frequencies.

#### Keywords

60 GHz phase shifter, 65 nm CMOS, Active circulator

### **1. INTRODUCTION**

Phase shifters are the devices used to adjust the transmission phase in a system. The main operation behind a phase shifter is it allows adjustment of insertion phase. They are widely used in the field of RF communication in phased arrays and in frequency translators. The performance of such systems greatly depend on the phase shifting component. Depending on the application one may require either an analog or digital phase shifter. The digital phase shifter provides a constant phase over a specific bandwidth and the analog phase shifter provides continuously controlled phase shift over a wide range of frequencies [1]. Various topologies have been proposed for the development of phase shifters [2]-[3]. The first topology is the distributed type phase shifter with loaded transmission lines is widely used due to its low insertion loss [4]. This technique requires transmission lines with lengths proportional to the signal wavelength. The major drawback in this approach is the large chip size. If we replace the transmission lines with active LC components the chip size can be reduced [5]. The second topology is the Forward Type phase shifter (FTPS) [6]-[7] which depend on couplers (transmission line) to split the input signal into multiple signals for processing and combine them at the output. This phase shifter requires many couplers for combining the multiple signals at the output, resulting in large chip area due to the presence of many passive couplers. The Third topology is the Reflective Type Phase Shifter (RTPS) [8]-[10] which is more compact since it uses the same coupler (transmission line) to split the signals and combine them at the output. The couplers can be replaced by active components in order to reduce the chip size. Phase shifters using spiral inductors exhibit high insertion loss and limited phase shift [11]. The passive couplers in the FTPS and RTPS can be replaced by active LC components to reduce the size of the phase shifter. The other topologies are loaded line phase shifter (LL) [12], switched line phase shifter (SL) [13] which exhibits large insertion loss and the high pass or low pass (HP/LP) phase shifter [14]. All these phase shifters have passive components in the form of couplers (transmission lines) which results in large chip size. While considering phase shifters working in 60 GHz, a digitally controlled phase shifter is developed [15] which involves the usage of transmission lines and exhibits insertion loss of 8.5 to 10.3 dB, return loss above 10 dB and phase range of 180°. A digitally controlled phase shifter in 60 GHz is developed in 65 nm CMOS with noise figure as 7.2 dB, phase shift range of 360° and chip area of 1.6mm<sup>2</sup> [16]. A phase shifter both passive and active in 60 GHz is designed with a phase shift range of 180° in passive phase shifter, insertion loss of 4.2 dB to 7.5 dB, noise figure of 16.5 dB and phase shift range of 360° in the active phase shifter [17]. Considering the chip size and performance, it is better to use active phase shifter with transmission lines replaced by lumped elements such as the LC network. At microwave frequencies, the continuous phase shift can be obtained by using RTPS with a varactor. For frequencies above 10 GHz it is not feasible to use analog phase shifters with varactors because the capacitance required for the phase shifter. Therefore, it is very difficult to find voltage controlled analog phase shifter for frequencies above 10 GHz [18].

In this paper, an analog phase shifter working at the frequency of 60 GHz is proposed and demonstrated experimentally in 65 nm bulk CMOS process for microwave frequency applications. Here we use an active circulator and a series LC network to make the circuit fully active and compact. This phase shifter is designed in such a way to attain a phase shift range of  $140^{\circ}$ . This proposed phase shifter exhibits low insertion loss over a high frequency band and low power consumption. The main advantage in using 65 nm bulk CMOS process is low cost, low insertion loss and high performance.

## 2. PROPOSED ANALOG PHASE SHIFTER

A circulator was proposed and demonstrated using bipolar transistors in the range of megahertz [19] in the year 1965. Later modifications were made and was designed for microwave frequencies with GaAs FETs with supply voltages above 10 V [20]. In later years the circulator was redesigned in 180 nm CMOS process for a supply voltage of 3.5 V and frequency of 2.4 GHz [21]. We have redesigned the circulator using 65 nm CMOS process for a frequency of 60 GHz and minimized the supply voltage to 1.2 V.

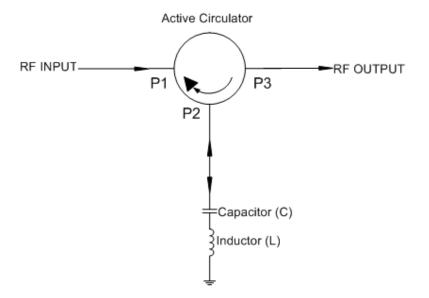

Figure.1 shows the block diagram of the proposed analog phase shifter. It is a phase shifter based on an active circulator consisting of three ports namely P1, P2 and P3. Active circulator is a three terminal device in which input from one port is transmitted to the next port in rotation. The circulator acts as an isolator between the input and the output signal so that phase shift is well observed. The RF input signal is given at P1 of the circulator from the left side. This signal from P1 is transmitted to P2. The LC components are in series with P2 which results in the desired phase shift and helps to reflect the signal to P3 at the right. At P3, we get the desired RF output. Desired phase shift can be attained by either tuning L or C connected to P2. Initially during simulation we have assumed that the active circulator and the LC elements are lossless. In order to find out the value of L and C, we have considered the following expression.

$$Z = j \left( \omega L - \frac{1}{\omega C} \right) \text{ where } \omega = 2\pi f \text{ . The resonant frequency is obtained by } f = \frac{1}{2\pi \sqrt{LC}}$$

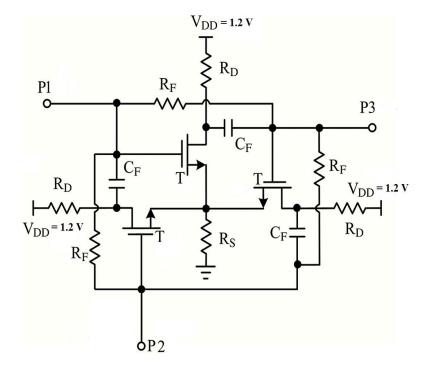

Figure. 2 shows the schematic diagram of the active circulator. The active circulator used in this circuit is a three port circulator. It has three nMOS transistors interconnected with each other.  $R_F$ ,  $R_D$ ,  $R_S$  and  $C_F$  play a major role in the working of the circuit. The three feedback resistors ( $R_F$ ) provides negative feedback in each transistor. The three feedback capacitors ( $C_F$ ) are used to link all the three transistors in an end to end fashion. The source resistor ( $R_S$ ) is shared among all the three transistors and one transistor is source coupled with the other two transistors using this source resistor. Three source degenerators are used in the circulator. The circuit works in a

symmetric fashion. The supply voltage  $(V_{DD})$  is given for each transistor. Same DC voltage is given in all ports of the circulator to bias the transistors.

Figure 1. Block diagram of proposed phase shifter

Figure 2. Schematic diagram of the active circulator

#### **3. SIMULATION RESULTS**

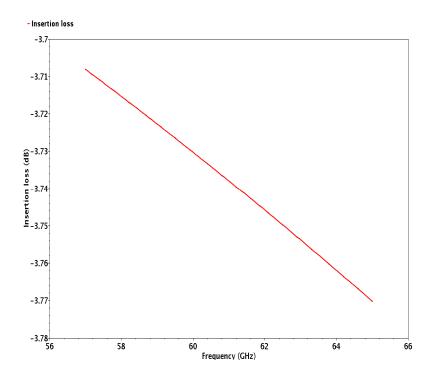

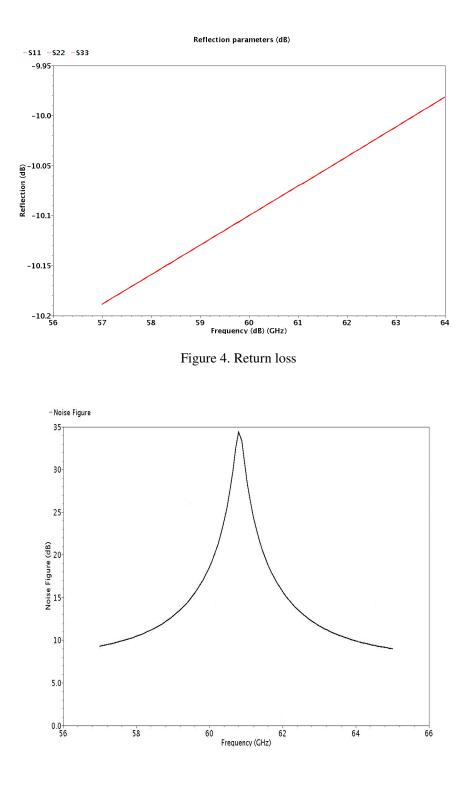

Figure.3 shows the insertion loss of the circulator. Considering the frequency range of 57 GHz to 65 GHz, the insertion loss is simulated and experimentally proved to be low. The insertion loss for this phase shifter is 3.7 dB for the frequency range of 60 GHz. Figure.4 shows the reflection parameters of the circulator. By further calculation, return loss is obtained as 20 dB. Since the circuit is working in a symmetric manner the input and output return loss are the same for the frequency range of 57 GHz to 65 GHz. The LC network has an inductance of approximately L = 74 pH and capacitance of approximately C = 95 fF. This results in a resonant frequency of 60 GHz. During simulation to attain phase shift the circuit is tuned for the transmission coefficients to get close to 0 dB and by varying the capacitance and inductance in the LC network the desired phase shift is attained. To characterize the linearity of this phase shifter the output power versus input power is measured and the input P1(dB) is 5.129 dB. The maximum power consumption for the circuit is 20 mW with a supply voltage of 1.2 V.

When compared with many topologies this proposed phase shifter consumes less power to give high performance due to scaling in technology size to 65 nm bulk CMOS Process. Figure.5 shows the noise figure for the desired frequency range which is 18.56 dB for 60 GHz. Phase shifters using active components have high noise figure than the phase shifters using passive components. Since the passive components include couplers using transmission lines they don't have much noise. While using active components like transistors, capacitors and resistors, the noise figure is higher. If the phase shifter is used in a receiver then the noise figure should be less. If this phase shifter is used in a transmitter then high noise figure is negligible.

Figure 3. Insertion loss

Figure 5. Noise Figure

| Table 1. Performance summary of the phase smiller |                 |

|---------------------------------------------------|-----------------|

| Technology                                        | 65 nm bulk CMOS |

|                                                   |                 |

| Frequency (GHz)                                   | 60              |

|                                                   |                 |

| Max.insertion loss (dB)                           | 3.73            |

|                                                   |                 |

| Power consumption (mW)                            | 20              |

|                                                   |                 |

| Noise figure (dB)                                 | 18.56           |

| (db)                                              | 10.00           |

| Input D1dD (dDm)                                  | 5.129           |

| Input P1dB (dBm)                                  | 5.129           |

|                                                   |                 |

| Return loss (dB)                                  | 20              |

|                                                   |                 |

| Phase shift range                                 | 140°            |

|                                                   |                 |

|                                                   |                 |

Table 1. Performance summary of the phase shifter

# **3.** CONCLUSION

This paper has presented the development of a 60 GHz phase shifter in 65 nm bulk CMOS technology. The phase shifter consists of an active circulator and a LC network. The circulator is very small with only three transistors which are connected end to end in a ring which makes the design more compact. This phase shifter exhibits low power consumption and low insertion loss. Return loss is 20 dB. Since the technology is more advanced than the most popular 180 nm technology, the performance is high enough for a phase shifter working at 60 GHz. This phase shifter exhibits a phase shift range of 140°.

# REFERENCES

- [1] Rosa R. Lahiji, Linda P.B. Katehi, Saeed Mohammadi, "A Distributed Analogue CMOS Phase Shifter with Shielded Transmission Line," *Proc.38th European Conf., Amsterdam, The Netherlands*, pp.817-820, Oct 2008.

- [2] K.Miyaguchi, M. Hieda, K.Nakahara, H.Kurusu, M.Nii, M.Kasahara, T.Takagi and S.Urasaki, "An ultra-broad- band reflection-type phase shifter MMIC with series and parallel LC circuits," *IEEE Trans Microw.Theory tech.*, ch. 49, no. 12, pp. 2446-2454, Dec. 2001.

- [3] D.Viveiros Jr., D. Consonni, and A.K.Jastrzebski, "A tunable all-pass MMIC active phase shifter," *IEEE Trans. Microw. Theory Tech.*, vol. 50, no. 8, pp.1885-1889, Aug. 2002.

- [4] A.S.Nagra and R.A.York," Distributed analog phase shifters with low insertion loss," *IEEE Trans. Microw. Theory Tech.*, ch.47, no. 8, pp.1885-1889, Aug. 2002.

- [5] C. Lu, A. V. Pham and D.Livezey, "Development of multiband phase shifters in 180-nm RF CMOS technology with active loss compensation," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 1, pp. 40-45, Jan.2006.

- [6] P.Y.Chen, T. W. Huang, H. Wang, Y. C.Wang, C.H. Chen, and P.C. Chao," K-band HBT and HEMT monolithic active phase shifters using vector sum method," *IEEE Trans. Microw. Theory Tech.*, vol.52, no. 5, pp. 1414-1424, May 2004.

- [7] P.- S. Wu, H.-Y. Chang, M.-D.T sai, T.-W. Huang, and H. Wang, "New miniature 15-20- GHz continuous-phase /amplitude control MMICs using 0.18-μm CMOS technology," *IEEE Trans. Microw Theory Tech.*, vol. 54, pp. 10-19, Jan. 2006.

- [8] H. Zarei and D. J. Allstot, "A low-loss phase shifter in 180nm CMOS for multiple- antenna receivers," *IEEE int. Solid-State Circuits Conf. Tech. Dig.*, vol. 1, pp.392-393, Feb. 2004.

- [9] H. Zarei, S. Kodama, C.T. Charles and D. J. Allstot, "Reflective- type phase shifters for multiple antenna transceivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 8, pp. 1647-1656, Aug. 2007.

- [10] F. Ellinger, R. Vogt and W. Bachtold, "Ultracompact reflective type phase shifter MMIC at Cband with 360° phase-control range for smart antenna combining," *IEEE J. Solid State Circuits*, vol. 37, no. 4, pp. 481-486, Apr. 2002.

- [11] F. Ellinger, R. Vogt, and W.Bachtold, "Ultra compact, low loss, varactor tuned phase shifter MMIC at C-band," *IEEE Microw. Wireless Compon. Lett.*, vol. 11, no. 3, pp. 104-105, Mar. 2001.

- [12] A.Natarajan, B, Floyd and A. Hajimili, "A bidirectional RF- combining 60 GHz phased array front-end," *IEEE Int.Solid-State Circuits Conf. Tech. Dig.*, pp. 202-203, Feb.2007.

- [13] D.W. Kang, H.D.Lee, C.H.Kim and S.Hong, "Ku- band MMIC phase Shifter using a parallel resonator with 0.18- μm CMOS technology," *IEEE Trans. Microw. Theory Tech.*, vol.54, no. 1, pp. 294-301, Jan. 2006.

- [14] M.A. Morton, J.P.Comeau, J.D. Cressler, M. Mitchell and J. Papapolymerou," Sources of phase error and design considerations for silicon-based monolithic high pass/low pass microwave phase shifters," *IEEE Trans. Microw.Theory Tech.*, vol. 54, no. 12, pp. 4032-4040, Dec. 2006.

- [15] Yikun Yu, Baltus, P., van Roermund, A. Jeurissen, D. de Graauw, A. van der Heijden, E. Pijper, R., "A 60GHz Digitally Controlled Phase Shifter in CMOS," *IEEE Solid-State Circuits Conference*, 2008, ESSCIRC 2008, 34th European., pp. 250 – 253, Sep. 2008.

- [16] Yikun Yu, Baltus, P., van Roermund, A. de Graauw, A. van der Heijden, E. Collados, M. Vaucher, C., "A 60 GHz digitally controlled RF-beamforming receiver front-end in 65 nm CMOS," *Radio Frequency Integrated Circuits Symposium*, 2009, *RFIC 2009, IEEE*., pp. 211-214, June. 2009.

- [17] Mind-Da Tsai, Natarajan A, "60 GHz passive and active RF-path phase shifters in silicon", *Radio Frequency Integrated Circuits Symposium*, 2009, *RFIC 2009, IEEE.*, pp.223-226, June. 2009.

- [18] Tae-Gyu Kim, Dong-Sik Woo, Chang-won Lee and Kang Wook Kim, "A new 40 GHz analog phase shifter using phase- locked loops," *IEEE European Microw.Conf.*, vol. 2, Oct. 2005.

- [19] S.Tanaka, N. Shimomura, and K.Ohtake, "Active circulators- The realization of circulators using transistors," *Proc. IEEE*, vol. 53, no. 6, pp. 260-267, Jun. 1965.

- [20] Y. Ayasli, "Field effect transistor circulators," *IEEE Trans Magn*, vol. 25, no. 5, pp. 3242-3247, Sep. 1989.

- [21] You Zheng and Carlos E. Saavedra, "An Ultra- Compact CMOS Variable Phase Shifter for 2.4-GHz ISM Application," *IEEE Trans on Microw Theory and Tech*, vol. 56, no. 6, pp. 1349-1354, Jun. 2008.

#### Authors

**ETB.Samuel Jigme Harrison** received the Bachelor of Engineering degree in Electronics and Communication from Anna University, Chennai, India in 2008. He is now pursuing Master of Science in Integrated Circuit Design, a joint degree offered by the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore and Technical University of Munich, Germany.

His research interests include Radio Frequency Circuit Design and Analog Design.

Yue ping Zhang received the B.E. degrees from the Taiyuan Polytechnic Institute, Taiyuan, China, in 1982, the M.E. degree from the Shanxi Mining Institute of Taiyuan University of Technology, Shanxi, China, in 1987, and the Ph.D. degree from the Chinese University of Hong Kong, Hong Kong, in 1995, all in electronic engineering. He is now an Associate Professor with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore. He leads the Micro Radio Group at the Integrated Systems Research Laboratory to develop radio technologies for wireless communications. He was a Guest Editor of the journal's Special Issue on RF and Microwave Subsystem Modules for Wireless Communications.

His research interests include propagation of radio waves, characterization of radio channels, miniaturization of antennas, design of RF ICs, and implementation of wireless communications systems.